Introduction & Market Context

The artificial intelligence revolution has fundamentally transformed computing requirements, driving unprecedented demand for specialized hardware capable of handling machine learning workloads. Traditional central processing units (CPUs), originally designed for sequential processing tasks, have proven inadequate for the parallel computational demands of modern AI applications. This technological shift has sparked a new era of innovation in processor design, where specialized chips and acceleration technologies are reshaping the entire computing landscape.

Machine learning workflows require massive parallel processing capabilities to handle matrix multiplications, tensor operations, and complex mathematical computations at scale. These requirements have catalyzed the development of purpose-built hardware architectures that can deliver orders of magnitude performance improvements over conventional processors. The global market for AI chips has experienced explosive growth, reaching $15.3 billion in 2023 and projected to exceed $85 billion by 2030, according to industry analysts.

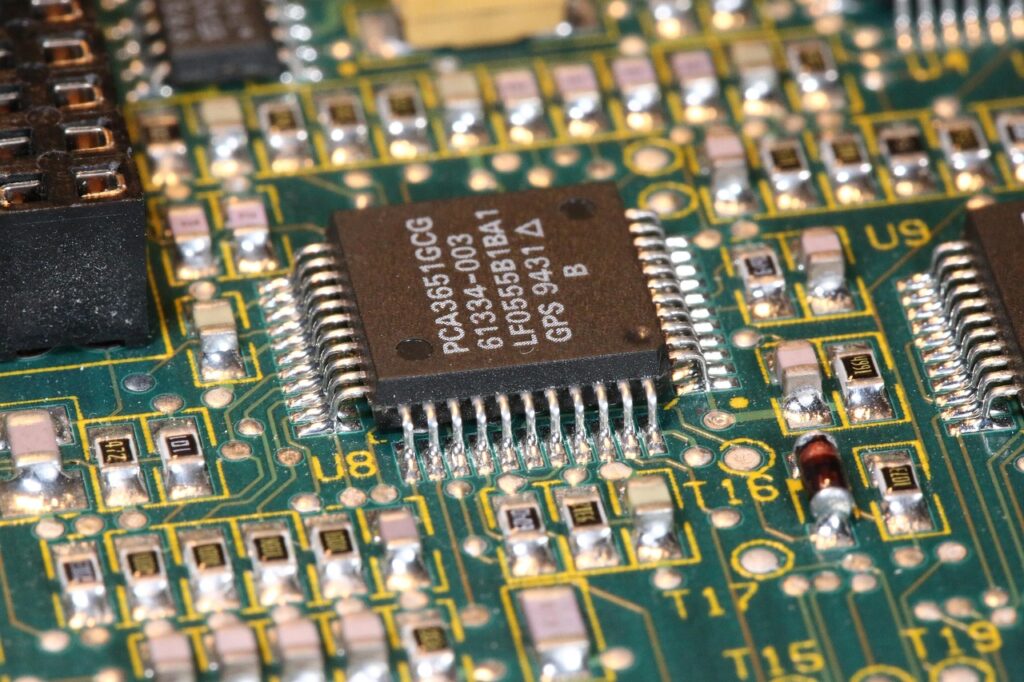

The hardware acceleration ecosystem encompasses multiple specialized processor types, each optimized for specific aspects of machine learning computation. Graphics Processing Units (GPUs) have emerged as the dominant force in training large neural networks, while newer architectures like Tensor Processing Units (TPUs), Field-Programmable Gate Arrays (FPGAs), and Application-Specific Integrated Circuits (ASICs) are addressing specialized use cases ranging from edge inference to high-throughput data center operations.

Major technology companies have invested billions of dollars in developing custom silicon solutions, recognizing that hardware optimization is crucial for maintaining competitive advantages in AI applications. Google’s TPU architecture, NVIDIA’s specialized GPU platforms, Intel’s neural processing units, and emerging startups like Cerebras and Graphcore are all contributing to a rapidly evolving hardware landscape that promises to unlock new possibilities in artificial intelligence and machine learning.

This transformation extends beyond pure performance metrics, encompassing energy efficiency, cost optimization, and deployment flexibility considerations that are reshaping how organizations approach AI infrastructure investments. The convergence of specialized hardware with advanced software frameworks is creating new paradigms for distributed computing, edge AI deployment, and real-time inference applications that were previously impossible to implement at scale.

Historical Evolution and Market Context

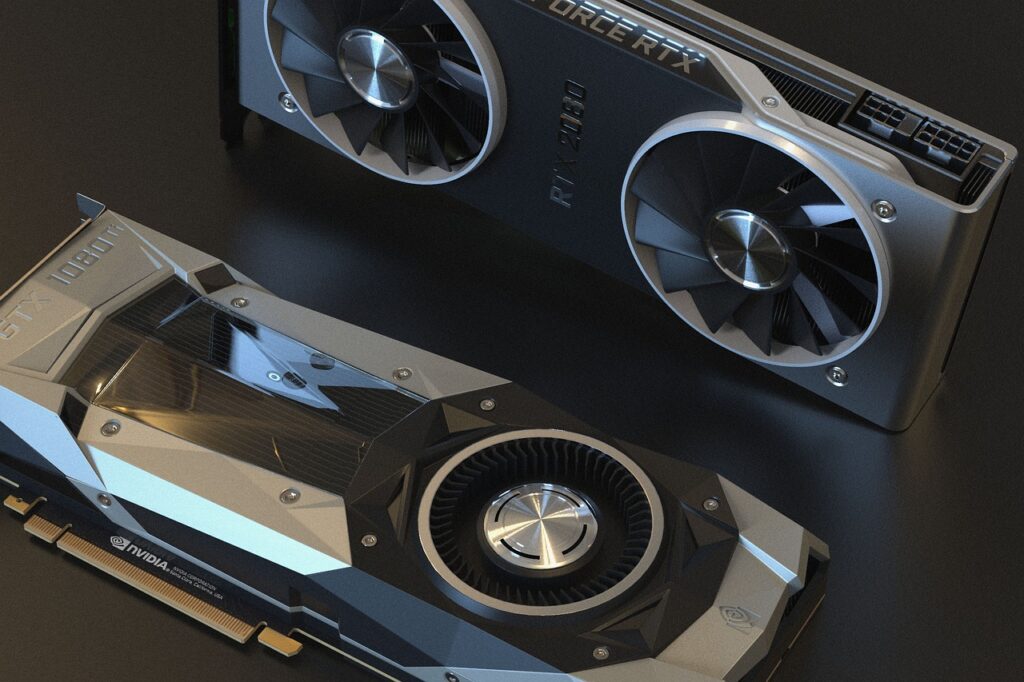

The journey toward specialized machine learning hardware began in the early 2010s when researchers discovered that graphics processing units, originally designed for rendering video game graphics, could accelerate neural network training through their parallel architecture. This serendipitous discovery marked the beginning of a fundamental shift in how the technology industry approached computational acceleration for AI applications.

NVIDIA’s CUDA programming platform, introduced in 2006, inadvertently became the foundation for GPU-accelerated machine learning. Researchers at Stanford and other institutions began leveraging CUDA-enabled GPUs to train neural networks significantly faster than traditional CPU-based approaches. The 2012 breakthrough achieved by Alex Krizhevsky’s ImageNet-winning AlexNet model, trained on NVIDIA GPUs, demonstrated the transformative potential of GPU acceleration for deep learning applications.

This initial success prompted NVIDIA to pivot toward AI-focused hardware development, introducing specialized features like Tensor Cores in their Volta architecture and developing comprehensive software ecosystems around machine learning acceleration. The company’s revenue from data center operations, primarily driven by AI applications, grew from $830 million in 2016 to over $15 billion in 2023, illustrating the massive market opportunity created by specialized ML hardware.

Google’s development of Tensor Processing Units represented another pivotal moment in ML hardware evolution. Recognizing that their internal workloads required custom optimization beyond what commercially available processors could provide, Google designed TPUs specifically for TensorFlow operations. The first-generation TPU, introduced in 2016, delivered 15-30x performance improvements over contemporary CPUs and GPUs for inference workloads, while consuming significantly less power.

The success of early GPU and TPU implementations inspired a wave of innovation across the semiconductor industry. Intel acquired Nervana Systems and Habana Labs to develop specialized neural processing units, while AMD expanded their GPU offerings to compete directly with NVIDIA’s AI-focused products. Simultaneously, a new generation of AI chip startups emerged, each proposing novel architectural approaches to machine learning acceleration.

Field-Programmable Gate Arrays gained renewed relevance in the ML hardware landscape due to their reconfigurable nature, allowing organizations to optimize hardware configurations for specific neural network architectures. Microsoft’s deployment of FPGAs across their Azure cloud infrastructure for AI acceleration demonstrated the viability of reconfigurable hardware for large-scale machine learning operations.

The emergence of edge AI applications created additional hardware requirements focused on power efficiency and compact form factors. Companies like Qualcomm, MediaTek, and Apple began integrating specialized neural processing units into mobile processors, enabling on-device AI capabilities for smartphones and IoT devices. This trend toward edge inference acceleration has become increasingly important as privacy concerns and latency requirements drive more AI processing to local devices.

Investment in AI chip startups reached record levels, with companies like Cerebras Systems raising hundreds of millions of dollars to develop wafer-scale processors, and Graphcore attracting significant funding for their Intelligence Processing Units. These specialized architectures challenge conventional assumptions about processor design, implementing novel approaches to memory hierarchy, interconnect topology, and computational parallelism optimized specifically for machine learning workloads.

Current Technology Landscape and Performance Analysis

Today’s machine learning hardware ecosystem represents a diverse array of specialized architectures, each optimized for different aspects of AI computation. Graphics Processing Units continue to dominate training workloads for large language models and computer vision applications, with NVIDIA’s H100 and upcoming H200 processors delivering unprecedented performance for transformer-based architectures. These GPUs incorporate advanced features like fourth-generation Tensor Cores, high-bandwidth memory, and NVLink interconnects that enable efficient scaling across multiple processors.

Performance benchmarks reveal dramatic improvements in computational efficiency when specialized hardware is properly matched to workload characteristics. Modern GPUs can achieve 2-3 orders of magnitude performance improvements over CPUs for training deep neural networks, while consuming proportionally less energy per computation. The NVIDIA H100, for example, delivers up to 30 petaflops of AI performance using mixed-precision arithmetic, representing a 6x improvement over the previous-generation A100 processor.

Tensor Processing Units have evolved through multiple generations, with Google’s TPU v4 pods delivering over 1.1 exaflops of AI compute performance. TPUs excel particularly in inference workloads and training applications that can leverage their specialized matrix multiplication units. The architecture’s tight integration with Google’s TensorFlow framework and custom interconnect technology enables efficient scaling across thousands of processors for the largest neural network training jobs.

Application-Specific Integrated Circuits represent the ultimate in hardware specialization, with companies developing custom chips optimized for specific neural network architectures or deployment scenarios. Tesla’s Full Self-Driving (FSD) chip exemplifies this approach, delivering 144 billion operations per second while consuming only 72 watts, specifically optimized for automotive neural network inference. Similarly, Apple’s Neural Engine processors in M-series chips provide dedicated acceleration for on-device machine learning tasks while maintaining excellent power efficiency.

Emerging architectures are pushing the boundaries of conventional processor design. Cerebras Systems’ wafer-scale processors eliminate traditional packaging constraints by implementing an entire neural network across a single silicon wafer, providing massive memory bandwidth and eliminating inter-chip communication bottlenecks. Graphcore’s Intelligence Processing Units implement a unique architecture optimized for sparse computations common in modern transformer models, achieving superior performance per watt for many natural language processing workloads.

Memory hierarchy optimization has become crucial for ML hardware performance, as data movement often represents the primary bottleneck in neural network computation. High-bandwidth memory technologies, processing-in-memory approaches, and novel interconnect architectures are addressing these challenges. Samsung’s processing-in-memory solutions and Intel’s upcoming Ponte Vecchio architecture exemplify industry efforts to minimize data movement overhead through architectural innovation.

Software ecosystem development has proven equally important as hardware innovation. CUDA’s dominance in GPU programming has created substantial competitive advantages for NVIDIA, while alternative frameworks like ROCm for AMD GPUs and Intel’s oneAPI initiative attempt to provide vendor-neutral development environments. The emergence of compiler technologies that can automatically optimize neural networks for different hardware targets is reducing the complexity of multi-platform deployment.

Cost-performance analysis reveals significant variations across different hardware options depending on workload characteristics. While high-end GPUs and TPUs excel for large-scale training applications, edge-focused processors provide superior economics for inference-heavy deployments. Organizations must carefully evaluate total cost of ownership, including power consumption, cooling requirements, and software licensing costs when selecting ML hardware platforms.

Advanced Architecture Innovations and Emerging Technologies

The next generation of AI hardware architectures is incorporating revolutionary design principles that fundamentally challenge traditional computing paradigms. Neuromorphic computing, inspired by biological neural networks, represents one of the most promising frontiers in AI hardware development. Intel’s Loihi processors and IBM’s TrueNorth chips implement event-driven computation models that can achieve extraordinary energy efficiency for certain classes of machine learning applications, particularly those involving temporal pattern recognition and adaptive learning.

Photonic computing emerges as another transformative technology, leveraging light-based computation to overcome the bandwidth and energy limitations of electronic processors. Companies like Lightmatter and Lightelligence are developing optical neural network accelerators that can perform matrix multiplications at the speed of light while consuming significantly less power than traditional electronic systems. These photonic processors show particular promise for large-scale transformer models and computer vision applications where massive parallel computations dominate the workload.

In-memory computing architectures are gaining traction as a solution to the von Neumann bottleneck that limits traditional processor performance. By performing computations directly within memory arrays, these systems eliminate the energy and time overhead associated with data movement between processing units and memory. Crossbar arrays using resistive memory technologies can implement neural network computations with analog precision, potentially achieving orders of magnitude improvements in energy efficiency for inference workloads.

Quantum-classical hybrid computing systems represent the cutting edge of AI hardware innovation. While fault-tolerant quantum computers remain years away, near-term quantum devices are already demonstrating advantages for specific optimization problems relevant to machine learning. Variational quantum algorithms and quantum-enhanced sampling techniques show promise for accelerating certain aspects of neural network training, particularly for problems involving complex optimization landscapes.

The integration of specialized AI accelerators into edge devices is driving innovations in ultra-low-power processor design. ARM’s Ethos processors, Qualcomm’s AI Engine, and Google’s Edge TPU demonstrate how machine learning capabilities can be embedded into battery-powered devices without compromising operational lifetime. These edge AI processors often incorporate novel techniques like approximate computing, dynamic voltage scaling, and adaptive precision to maximize energy efficiency.

Chiplet-based architectures are enabling new approaches to AI processor design by allowing companies to mix and match specialized processing elements optimized for different aspects of machine learning computation. AMD’s CDNA architecture and Intel’s Xe-HPC platforms demonstrate how modular chip designs can provide flexibility in scaling compute resources while optimizing manufacturing costs and yields.

Future Outlook and Strategic Implications

The trajectory of AI hardware development suggests continued acceleration in specialized processor innovation over the next decade. Industry analysts project that the total addressable market for AI chips will exceed $200 billion by 2030, driven by expanding applications in autonomous vehicles, robotics, healthcare, and scientific computing. This growth will likely catalyze further consolidation among semiconductor companies while simultaneously creating opportunities for startups with breakthrough architectural innovations.

Software-hardware co-design is becoming increasingly critical as the complexity of AI applications grows. The tight coupling between neural network architectures and underlying hardware capabilities means that future AI systems will require unprecedented collaboration between software developers and hardware engineers. This trend is already evident in projects like Google’s EfficientNet models, specifically designed to maximize performance on TPU architectures, and Tesla’s neural network designs optimized for their custom FSD chips.

Sustainability considerations are driving new requirements for energy-efficient AI hardware. As machine learning workloads consume an increasing share of global electricity, processor designers must balance performance improvements with environmental impact. This has led to renewed interest in analog computing approaches, neuromorphic architectures, and novel cooling technologies that can reduce the carbon footprint of large-scale AI deployments.

The geopolitical implications of AI hardware development are reshaping global technology supply chains. Export controls on advanced semiconductors, concerns about technological sovereignty, and the strategic importance of AI capabilities are driving countries to invest heavily in domestic chip manufacturing capabilities. This trend may lead to the fragmentation of global AI hardware markets and accelerate innovation as different regions pursue independent technological development paths.

Edge AI deployment will continue driving demand for specialized low-power processors optimized for inference workloads. The proliferation of IoT devices, autonomous systems, and privacy-focused applications requiring on-device computation will create massive markets for efficient AI accelerators. This trend will likely favor architectures that can adapt to diverse workloads while maintaining strict power and thermal constraints.

The convergence of AI hardware with emerging technologies like 6G wireless networks, quantum sensors, and brain-computer interfaces will create new application domains requiring novel processor architectures. These interdisciplinary challenges will drive continued innovation in specialized computing systems optimized for specific AI applications.

Conclusion and Investment Recommendations

The transformation of computing infrastructure through AI-specialized hardware represents one of the most significant technological shifts since the advent of the microprocessor. Organizations planning AI deployments must carefully evaluate their hardware strategies, considering factors beyond pure performance metrics to include total cost of ownership, software ecosystem maturity, and long-term scalability requirements.

For enterprises embarking on AI initiatives, the choice of hardware platform can fundamentally impact both short-term project success and long-term competitive positioning. Cloud-based AI services provide access to cutting-edge hardware without capital investment, while on-premises deployments offer greater control and potentially lower operational costs for sustained workloads.

The rapid pace of innovation in AI hardware suggests that organizations should prioritize flexibility and avoid over-committing to specific architectures without clear migration strategies. The most successful AI implementations will likely leverage hybrid approaches that combine different processor types optimized for specific aspects of machine learning workflows.

Investment in AI hardware infrastructure should be viewed as a strategic capability rather than a simple technology upgrade. The organizations that successfully navigate this hardware transition will gain substantial competitive advantages in their ability to deploy sophisticated AI applications at scale, while those that lag behind may find themselves increasingly disadvantaged in an AI-driven economy.

The convergence of specialized hardware, advanced software frameworks, and emerging technologies like quantum computing promises to unlock AI capabilities that are difficult to imagine today. Understanding and preparing for these technological shifts will be crucial for organizations seeking to harness the full potential of artificial intelligence in their operations and strategic planning.